Test that ASC can communicate with GPIOs. More...

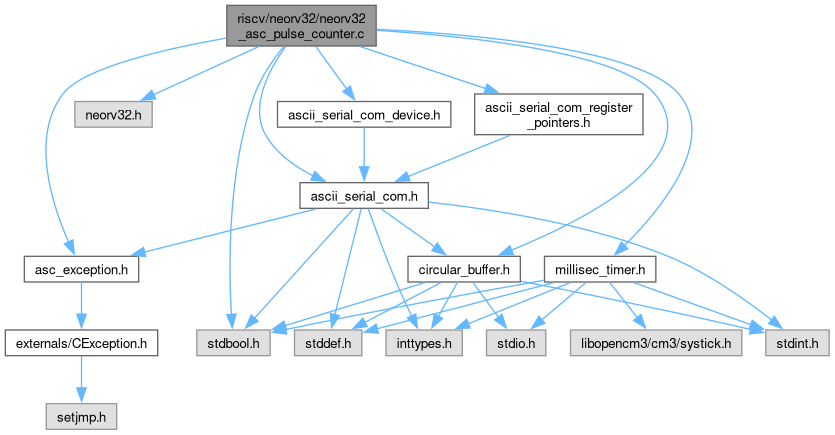

#include <stdbool.h>#include <neorv32.h>#include "asc_exception.h"#include "ascii_serial_com.h"#include "ascii_serial_com_device.h"#include "ascii_serial_com_register_pointers.h"#include "circular_buffer.h"#include "millisec_timer.h"

Go to the source code of this file.

Macros | |

| #define | BAUD_RATE 19200 |

| #define | UART1_TX_BUFFER_FULL ((NEORV32_UART1.CTRL & (1 << UART_CTRL_TX_FULL)) != 0) |

| #define | nRegs 6 |

Functions | |

| DECLARE_ASC_DEVICE_W_REGISTER_POINTERS () uint8_t tmp_byte | |

| int | main () |

Variables | |

| CEXCEPTION_T | e |

| uint16_t | nExceptions |

| volatile REGTYPE * | register_map [nRegs] |

| Register Map. | |

| REGTYPE | register_write_masks [nRegs] |

| Write masks for register_map. | |

| int | rx_status |

Detailed Description

Test that ASC can communicate with GPIOs.

Register map is documented at register_map

Definition in file neorv32_asc_pulse_counter.c.

Macro Definition Documentation

◆ BAUD_RATE

| #define BAUD_RATE 19200 |

Definition at line 27 of file neorv32_asc_pulse_counter.c.

◆ nRegs

| #define nRegs 6 |

Definition at line 34 of file neorv32_asc_pulse_counter.c.

◆ UART1_TX_BUFFER_FULL

| #define UART1_TX_BUFFER_FULL ((NEORV32_UART1.CTRL & (1 << UART_CTRL_TX_FULL)) != 0) |

Definition at line 28 of file neorv32_asc_pulse_counter.c.

Function Documentation

◆ DECLARE_ASC_DEVICE_W_REGISTER_POINTERS()

| DECLARE_ASC_DEVICE_W_REGISTER_POINTERS | ( | ) |

Definition at line 155 of file stm32f091nucleo64_adc_streaming.c.

◆ main()

| int main | ( | void | ) |

Definition at line 80 of file neorv32_asc_pulse_counter.c.

Variable Documentation

◆ e

| CEXCEPTION_T e |

Definition at line 31 of file neorv32_asc_pulse_counter.c.

◆ nExceptions

| uint16_t nExceptions |

Definition at line 32 of file neorv32_asc_pulse_counter.c.

◆ register_map

| volatile REGTYPE* register_map[nRegs] |

Register Map.

Register Map

| Register Number | Description | r/w |

|---|---|---|

| 0 | GPIO output (lower 32 bits) | r/w |

| 1 | GPIO output (upper 32 bits) | r/w |

| 2 | GPIO input (lower 32 bits) | r |

| 3 | GPIO input (upper 32 bits) | r |

| 4 | Pulse counter count | r |

| 5 | Pulse counter CSR* | r/w |

Pulse counter CSR:

Bit 0: enable Bit 1: reset

- See also

- register_write_masks

Definition at line 57 of file neorv32_asc_pulse_counter.c.

◆ register_write_masks

| REGTYPE register_write_masks[nRegs] |

Write masks for register_map.

These define whether the given register in register_map is writable or not

Definition at line 71 of file neorv32_asc_pulse_counter.c.

◆ rx_status

| int rx_status |

Definition at line 78 of file neorv32_asc_pulse_counter.c.